## AN13120

# How to use SSARC to configure a peripheral after wake up on RT1170

Rev. 0 — February 3, 2021 Application Note

### 1 Introduction

The i.MX RT1170 crossover processor sets the speed records at 1 GHz. This ground-breaking family combines superior computing power and multiple media capabilities with more usability as well as real-time functionality.

This application note introduces how to use SSARC to configure a peripheral after wake-up.

The hardware is based on RT1170 EVK RevC1 (Hereafter referred to as EVK) and software is based on SDK 2.9.0 with IAR IDE.

### 2 SSARC overview

The State Save and Restore Controller (SSARC) saves the registers of functional modules in a memory, located in LPSR domain, before powering down and restoring the registers from memory after the module is powered up. This module is able to configure a peripheral before the CPU wakes up. Once the CPU wakes up, it can use the peripheral without initialization. Figure 1 shows the basic functions of SSRAC.

### 2.1 Descriptor

Figure 1. SSARC basic function and work flow

Descriptor is the most basic element in SSARC. It has up to 1024 descriptors which support most operations like CPU, such as write, read, delay and polling. It supports four operations and seven types of operation.

#### Contents

| 1   | Introduction                                              | .1 |

|-----|-----------------------------------------------------------|----|

| 2   | SSARC overview                                            | 1  |

| 2.1 | Descriptor                                                | .1 |

| 2.2 | Group                                                     | 2  |

| 3   | Restore sequence and skills                               | 5  |

| 3.1 | Clock source for a peripheral                             | 5  |

| 3.2 | Restore method and sequence                               | 6  |

| 4   | Example                                                   | 6  |

|     |                                                           |    |

| 4.1 | Configure BPC2 as save and                                |    |

| 4.1 | Configure BPC2 as save and restore trigger source         | 6  |

| 4.1 | •                                                         |    |

|     | restore trigger source                                    |    |

|     | restore trigger source<br>Restore a GPIO pin after wakeup | 6  |

2/11

#### · Operations

- Save Disable and Restore Disable

- Save Enable and Restore Disable

- Save Disable and Restore Enable

- Save Enable and Restore Enable

#### · Type of operation

- Read Value and Write Back

- Write a Fixed Value

- Read a register or with a value then write it back (OR)

- Read a register and with a value then write it back (AND)

- Delay several cycles (Delay)

- Read a register until the bit or bits in it changed to 0 (Polling 0)

- Read a register until the bit or bits in it changed to 1 (Polling 1)

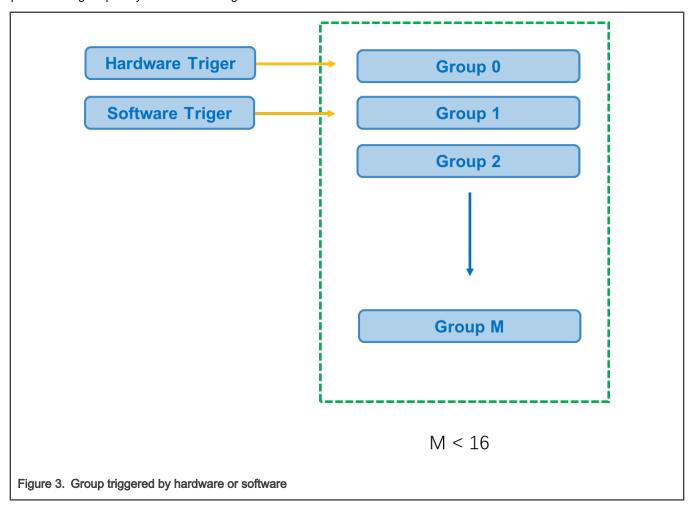

### 2.2 Group

The 1024 descriptors falls into 16 groups, with each group containing a number of continuous descriptors. The descriptor is controlled by group. The group can be trigger by either software or hardware. Each group has its own priority for save and restore.

How to use SSARC to configure a peripheral after wake up on RT1170, Rev. 0, February 3, 2021

Application Note

There are 16 priority settings from 0 to 15 and 0 has the highest priority. Usually the priority is not required to be cared about during the save operation but it is important for the restore operation. For example, if to use pins for a peripheral, the initialization of the pins has a higher priority than other settings.

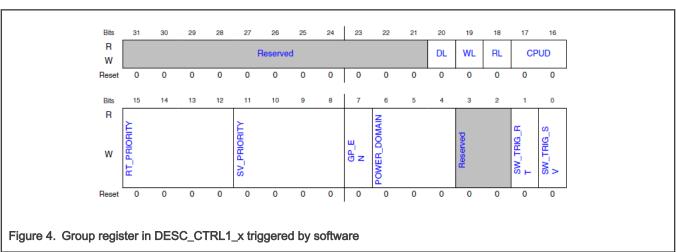

### 2.2.1 Group triggered by software

The software trigger method can be used to verify whether the SSARC settings are correct or not before entering low power. The bit 0 and bit 1 in  $\texttt{DESC\_CTRL1\_x}$ , x representing index for each group, are able to use the software to trigger the save and restore operations.

Application Note 3/11

Besides, the API as below can be used for save and restore operations.

void SSARC\_TriggerSoftwareRequest(SSARC\_LP\_Type \*base, uint8\_t groupID, ssarc\_software\_trigger\_mode\_t mode)

There is one software trigger example in SDK as below:

boards\evkmimxrt1170\driver\_examples\ssarc\software\_trigger

### 2.2.2 Group triggered by hardware

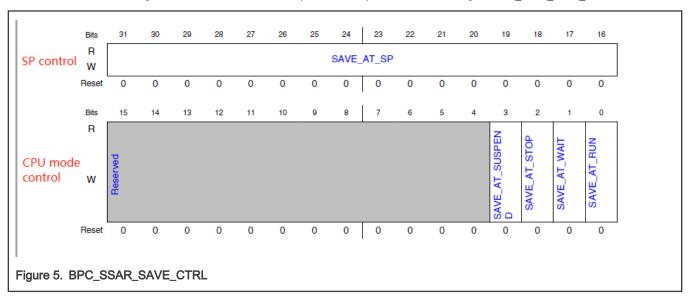

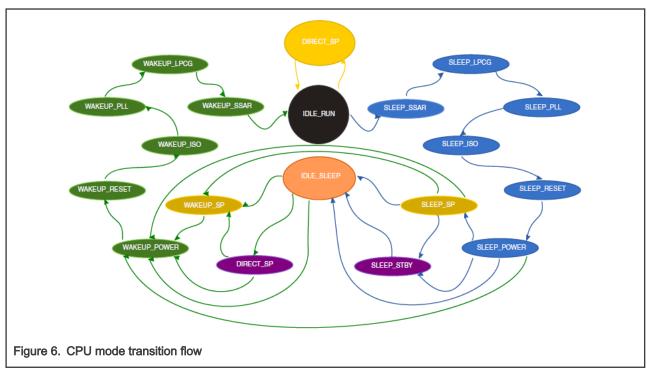

The group is able to triggered by BPC. When a power domain is powered off, the settings of this domain are lost. If it happens, SSARC automatically saves the data before power-off and restores the data after power-on. The BPC sends save and restore request to SSARC and completes the handshake. Because SP and CPU mode can trigger the BPC power-down, the trigger signal can be sent by SP or CPU mode.

Take BPC2, WAKEUP MIX with SP mode as example, usually the WAKEUP MIX is powered down after SP11. Once the SP switches to SP11 or other SP after SP11, BPC sends the save request to SSARC, the Group will be triggered by it and execute the operations in descriptors. If the SP switched to an SP, such as SP1, once the SP has been switched, the BPC2 will send the restore request to SSARC, then the SSARC will execute the restore operations in descriptors.

If BPC0, MEGA MIX, is controlled by CM7's CPU mode, once the CM7 entered a low power mode BPC0 will send the save request to SSARC. If the CM7 wake up, BPC0 will send the restore request to SSARC. For the low power mode, it can be WAIT, STOP or SUSPEND, but entering such mode will send the request that depends on the settings in BPC SSAR SAVE CTRL.

The registers BPC\_SSAR\_SAVE\_CTRL and BPC\_SSAR\_RESTORE\_CTRL can control the SSAR request. The register BPC SSAR ACK CTRL can be used to control the delay and wait response behavior.

Table 1. Power controller assignment

| Power domain | Assignment  |

|--------------|-------------|

| BPC0         | MEGA MIX    |

| BPC1         | DISPLAY MIX |

| BPC2         | WAKEUP MIX  |

| BPC3         | LPSRMIX     |

Table continues on the next page...

Application Note 4 / 11

Table 1. Power controller assignment (continued)

| Power domain | Assignment |

|--------------|------------|

| BPC4         | MIPIPHY    |

| BPC5         | Virtual    |

| BPC6         | Virtual    |

| BPC7         | Virtual    |

NOTE

Virtual power domains do not physically exist, but are used to trigger SSARC to save and restore, status and data.

### 3 Restore sequence and skills

### 3.1 Clock source for a peripheral

Because most use cases for SSARC relates with low power, the first step is to check the clock. The basic steps is as below.

- 1. Check whether the clock source for clock root is available or not in the target wakeup SP.

- 2. Check the LPCG status. LPCG can be controlled by SP or CPU mode.

- If LPCG is controlled by SP, just check whether it is available or not in the target wakeup SP.

- If LPCG is controlled by CPU mode, check the sleep CPU mode settings.

- 3. As shown in Figure 6, the last step of wakeup flow is CPU mode. When SSARC is going to initialize or restore a peripheral, the LPCG may block the clock, because the CPU is still under low power mode. Therefore, make sure the LPCG is available under a low power mode.

Application Note 5 / 11

For more detailed steps, see **Section 4.13** in *Debug and Application for RT1170 Clock and Low Power Feature* (document AN13104).

### 3.2 Restore method and sequence

As shown in Descriptor, there are seven types of operation descriptor. For different peripheral, different types of operations are needed. For example, for a GPIO PIN, use the Read Value and Write Back with save and restore function enabled, because the initialization of GPIO does not need to consider the order of operations while a peripheral needs. The basic flow is:

- Restore the PIN with IOMUXC\_SW\_MUX\_CTRL register and IOMUXC\_SW\_PAD\_CTRL register. These registers usually can use

the Read Value and Write Back with save and restore function enabled.

- Check the peripheral initialization sequence. Some peripherals need to initialize in the order of time. For example, FlexSPI needs to configure the peripheral to the run modem, configure the control register, unlock LUT table, update the LUT, and finally lock the LUT. Therefore, the tore function of FlexSPI is most for initialization. For these peripherals, it is a better operation to write a Fixed Value with save and restore function disabled.

### 4 Example

There are two examples to show how to use SSARC to restore a peripheral after wake up. Taking FlexSPI as examples, the low power mode is SP11 Suspend STBY. Under SP11 WAKEUP MIX will power down, which means its peripherals will also power down. The FlexSPI used in the example belongs to WAKEUP MIX. After wakeup, CPU runs at SP1 when the WAKEUP MIX is power on and CPU jumps to a running test function located at the FlexSPI address and toggles a GPIO with LED.

For how to jump to this test function, see **Chapter 4.15** in *Debug and Application for RT1170 Clock and Low Power Feature* (document AN13104).

### 4.1 Configure BPC2 as save and restore trigger source

Configure the BPC as SP control mode and send the save and restore request based on the SP settings. PD\_WKUP\_SP\_VAL is 0xf800, which means WAKEUP MIX will power down at SP11-SP15.

```

PGMC_BPC2->BPC_SSAR_SAVE_CTRL &= ~PGMC_BPC_BPC_SSAR_SAVE_CTRL_SAVE_AT_SP_MASK;

PGMC_BPC2->BPC_SSAR_SAVE_CTRL |= PGMC_BPC_BPC_SSAR_SAVE_CTRL_SAVE_AT_SP(PD_WKUP_SP_VAL);

PGMC_BPC2->BPC_SSAR_RESTORE_CTRL &= ~PGMC_BPC_BPC_SSAR_RESTORE_CTRL_RESTORE_AT_SP_MASK;

PGMC_BPC2->BPC_SSAR_RESTORE_CTRL |= PGMC_BPC_BPC_SSAR_RESTORE_CTRL_RESTORE_AT_SP(~PD_WKUP_SP_VAL);

```

Figure 7. Configure BPC2 as the save and restore trigger source

### 4.2 Restore a GPIO pin after wakeup

There is an on-board LED which connected to <code>GPIO\_AD\_04</code> on RT1170 EVK. This pin is used to toggle LED blinking. The GPIO in <code>GPIO\_AD\_04</code> is <code>GPIO09\_IO03</code>. For the pad and pin settings, the Read Value and Write Back with save enable and restore enable operation can be used.

- Add a descriptor for <code>IOMUXC\_SW\_MUX\_CTL\_PAD\_GPIO\_AD\_04</code>.

- Add a descriptor for  ${\tt IOMUXC\_SW\_PAD\_CTL\_PAD\_GPIO\_AD\_04}.$

- Add a descriptor for GPIO9\_GDIR, which is used to configure the direction register as output for toggle LED.

Application Note 6 / 11

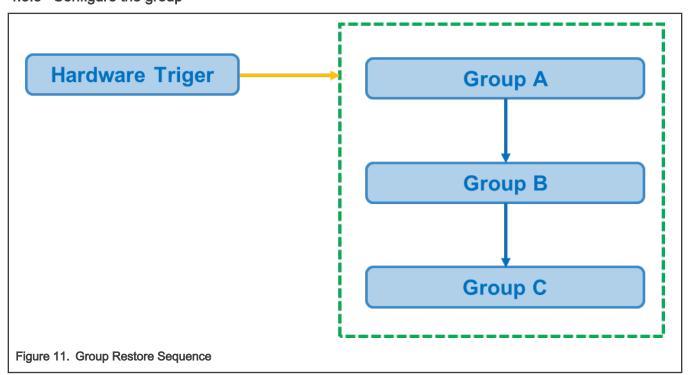

These three descriptors form a group, named as **Group A** in this applictaion note, which can be triggered by BPC2. After the system wakes up, the GPIO9 IO03 is restored and the register is toggled to enable the LED blink.

BOARD USER LED GPIO->DR TOGGLE = 1<<BOARD USER LED GPIO PIN;

### 4.3 Restore FlexSPI after wakeup

### 4.3.1 Restore the PIN settings

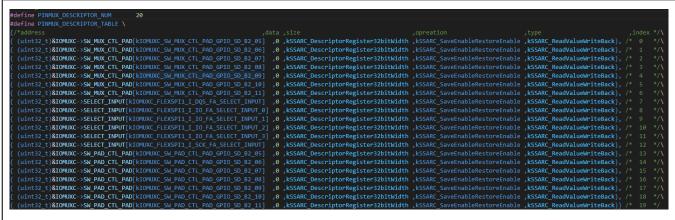

The first step to restore FlexSPI is that restore the <code>IOMUXC\_SW\_MUX\_CTRL</code>, <code>IOMUXC\_SW\_PAD\_CTRL</code> and the <code>SELECT\_INPUT</code> for function pin. Not all pins need to configure the <code>SELECT\_INPUT</code>, but all need to configure <code>IOMUXC\_SW\_MUX\_CTRL</code> and <code>IOMUXC\_SW\_PAD\_CTRL</code>. For pins restore Read Value and Write Back with save enable and restore enable operation can be used. The descriptors form a group, as shown in Figure 9, named as **Group B** in this application note.

Figure 9. Add descriptor for each pin IOMUXC\_SW\_MUX\_CTRL, IOMUXC\_SW\_PAD\_ACTRL and SELECT\_INPUT

#### 4.3.2 Restore the FlexSPI

Because the WAKEUP MIX is power down, FlexSPI needs to initialize again. To achieve that, the simple save and restore cannot be used because there are timing requirements in the configuration process. For example, it should be configured under run mode, it needs software reset and when configure the Look Up Table (LUT), it needs to enter a key and then unlock and lock the LUT. During the configuration process, some flag bits are needed to determine whether the working state is stable by polling. So that Read Value and Write Back with save enable and restore enable operation is unable to restore the FlexSPI. For how to configure the FlexSPI, see AN13112. Figure 10 shows the FlexSPI restore flow with different operation types and these descriptor forms a group, named as Group C in this application note.

Application Note 7/11

### 4.3.3 Configure the group

Several descriptors can form a group and then the group can be triggered by hardware or software. The restore priority is an important setting, because it impacts the restore sequence. Usually, the PIN restore should be the first step followed by the

How to use SSARC to configure a peripheral after wake up on RT1170, Rev. 0, February 3, 2021

Application Note 8 / 11

peripheral. For this example, Group A has the highest priority, Group B has the second highest priority, and the priority for Group C is the lowest.

```

groupConfig.startIndex = descriptorIndex;

for (i = 0; i < SSARC LED NUM; i++)

SSARC SetDescriptorConfig(SSARC HP, descriptorIndex++, &ssarc led[i]);

groupConfig.endIndex

= descriptorIndex - 1;

groupConfig.highestAddress = 0xFFFFFFFFU;

groupConfig.lowestAddress = 0x000000000U;

groupConfig.saveOrder

= kSSARC ProcessFromStartToEnd;

= 0U;

groupConfig.savePriority

groupConfig.restoreOrder = kSSARC_ProcessFromStartToEnd;

groupConfig.restorePriority = 0U;

groupConfig.powerDomain = kSSARC_WAKEUPMIXPowerDomain;

groupConfig.cpuDomain = kSSARC CM7Core;

SSARC_GroupInit(SSARC_LP, groupIndex++, &groupConfig);

groupConfig.startIndex = descriptorIndex;

```

Figure 12. Group A settings with Restore Priority 0

Figure 13. Group B settings with Restore Priority 1

```

groupConfig.startIndex = descriptorIndex;

for (i = 0; i < PINMUX DESCRIPTOR NUM; i++)</pre>

SSARC SetDescriptorConfig(SSARC HP, descriptorIndex++, &pinmuxDescriptor[i]);

groupConfig.endIndex

= descriptorIndex - 1;

groupConfig.highestAddress = 0xFFFFFFFFU;

groupConfig.lowestAddress = 0x000000000U;

groupConfig.saveOrder

= kSSARC ProcessFromStartToEnd;

groupConfig.savePriority = 0U;

groupConfig.restoreOrder = kSSARC ProcessFromStartToEnd;

groupConfig.restorePriority = 10;

groupConfig.powerDomain

= kSSARC WAKEUPMIXPowerDomain;

groupConfig.cpuDomain

= kSSARC CM7Core;

SSARC_GroupInit(SSARC_LP, groupIndex++, &groupConfig);

```

How to use SSARC to configure a peripheral after wake up on RT1170, Rev. 0, February 3, 2021

```

groupConfig.startIndex = descriptorIndex;

for (i = 0; i < FLEXSPI_DESCRIPTOR_NUM; i++)</pre>

SSARC SetDescriptorConfig(SSARC HP, descriptorIndex++, &flexspiDescriptor[i]);

groupConfig.endIndex

= descriptorIndex - 1;

groupConfig.highestAddress = 0xFFFFFFFFU;

groupConfig.lowestAddress = 0x000000000U;

groupConfig.saveOrder

= kSSARC ProcessFromStartToEnd;

groupConfig.savePriority

= 0U:

groupConfig.restoreOrder = kSSARC_ProcessFromStartToEnd;

groupConfig.restorePriority = 2U;

groupConfig.powerDomain = kSSARC_WAKEUPMIXPowerDomain;

groupConfig.cpuDomain

= kSSARC CM7Core;

SSARC GroupInit(SSARC_LP, groupIndex++, &groupConfig);

Figure 14. Group C settings with Restore Priority 2

```

These groups are triggered according to the priority. Then, FlexSPI is restored before the CPU wakes up. Once the CPU wakes up, CPU can acquire and execute instructions from Flash by FlexSPI and LED can be toggled by the GPIO toggle function.

How to use SSARC to configure a peripheral after wake up on RT1170, Rev. 0, February 3, 2021

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

**Right to make changes** - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX,EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE, VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, elQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: February 3, 2021

Document identifier: AN13120