# AN13386

# RT600 Flash Loader For Custom Flash Device

Rev. 0 — 01 September 2021 Application Note

#### 1 Introduction

The RT600 is a family of dual-core microcontrollers for embedded applications featuring an Arm® Cortex® -M33 CPU combined with a Cadence Xtensa HiFi4 advanced Audio Digital Signal Processor CPU. The RT600 provides up to 4.5 MB of on-chip SRAM (plus an additional 128 KB of tightly coupled HiFi4 ram) and several high-bandwidth interfaces to access off-chip flash. The FlexSPI flash interface supports two channels and includes a 32 KB cache and an on-the-fly decryption engine. The RT600 is designed to allow the Cortex-M33 to operate at frequencies of up to 300 MHz and the HiFi4 DSP to operate at frequencies of up to 600 MHz.

#### Contents

| 1 | Introduction                    | 1  |

|---|---------------------------------|----|

| 2 | Boot features                   | 1  |

| 3 | Boot settings                   | 1  |

| 4 | Hardware modifications          |    |

| 5 | Flash loader modifications      | 5  |

| 6 | Conclusion                      | 15 |

| 7 | References                      | 15 |

| 8 | Revision history                | 16 |

| Α | Required options, settings, and |    |

|   | modifications                   | 16 |

|   |                                 |    |

#### 2 Boot features

Since the RT600 has no internal flash for code and data storage, images must be stored elsewhere for loading upon reset or the CPU can execute-in-place(XIP) from external memory. Images can be loaded into on-chip SRAM from external flash or downloaded via the serial ports (UART, SPI, I2C, or USB). The code is then validated, and boot ROM jumps to on-chip SRAM.

The evaluation kit for the RT600 uses an octal flash connected to port B as an option for booting in addition to the pSRAM connected to port A. This document describes the necessary steps to boot from port A using the MIMXRT685-EVK with different external memories.

### 3 Boot settings

Depending on the values of the OTP bits, ISP pins, and the image header type definition, the bootloader decides whether to download code into the on-chip SRAM or run from external memory. The bootloader checks the OTP bit settings first, and then the ISP pins. If bits [3:0] in OTP word BOOT\_CFG [0] are not programmed (4b'0000), the boot source is determined by the states of the ISP boot pins (PIO1\_15, PIO1\_16, and PIO1\_17) as shown in Table 1. The focus in this application note is boot mode: FLEXSPI BOOT PORT A.

Table 1. Boot mode and ISP Downloader modes based on ISP pins

| Boot mode              | ISP2 pin<br>PIO1_17 | ISP1 pin<br>PIO1_16 | ISP0 pin<br>PIO1_15 | Description                                                                                                                                                                                                                                     |

|------------------------|---------------------|---------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                      | LOW                 | LOW                 | LOW                 | Reserved                                                                                                                                                                                                                                        |

| SDIO 0 (SD<br>CARD)    | LOW                 | LOW                 | HIGH                | Boot from an SD card device connected to SDIO 1 interface. The RT6xx looks for a valid image in the SD card device. If there is no valid image found, the RT6xx enters the ISP boot mode based on OTP DEFAULT_ISP_MODE bits (6:4, BOOT_CFG[0]). |

| FLEXSPI<br>BOOT PORT B | LOW                 | HIGH                | LOW                 | Boot from Quad or Octal SPI Flash devices connected to the FlexSPI interface 0 Port B. The RT6xx looks for a valid image in external Quad/Octal SPI Flash device.                                                                               |

Table continues on the next page...

Table 1. Boot mode and ISP Downloader modes based on ISP pins (continued)

|                                           |      |      |      | If there is no valid image found, the RT6xx enters recovery boot or ISP boot mode.                                                                                                                                                                     |

|-------------------------------------------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLEXSPI<br>BOOT PORT A                    | LOW  | HIGH | HIGH | Boot from Quad/Octal SPI Flash devices connected to the FlexSPI interface 0 Port A. The RT6xx looks for a valid image in external Quad/Octal SPI Flash device.                                                                                         |

|                                           |      |      |      | If there is no valid image found, the RT6xx enters recovery boot or ISP boot mode.                                                                                                                                                                     |

| SDIO 0<br>(eMMC)                          | HIGH | LOW  | LOW  | Boot from an eMMC device conncted to SDIO O interface. The RT6xx looks for a valid image in the eMMC device. If there is no valid image found, the RT6xx enters the ISP boot mode based on the value of OTP DEFAULT_ISP_MODE bits (6:4, BOOT_CFG [0]). |

| -                                         | HIGH | LOW  | HIGH | Reserved                                                                                                                                                                                                                                               |

| SERIAL ISP<br>(UART,SPI,<br>I2C, USB-HID) | HIGH | HIGH | LOW  | The Serial Interface (UART, SPI, and I2C,USB-HID) is used to program OTP, external Flash, SD or eMMC device.                                                                                                                                           |

| 111                                       | HIGH | HIGH | HIGH | Serial Master boot (SPI Slave, I2C Slave, or UART, USB-HID) is used to download a boot image over the serial interface (SPI Slave, I2C Slave or UART, USB-HID)                                                                                         |

### 4 Hardware modifications

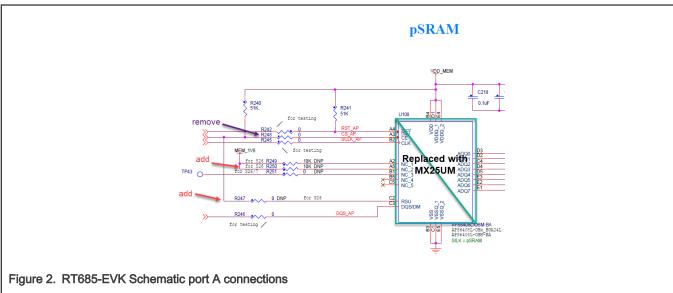

This section provides an overview on replacing the pSRAM with with a flash device and changing ISP pins to select FlexSPI Port A.

#### 4.1 Replacing the pSRAM with a flash device

The footprint of the evaluation board for port A supports the memories listed below; however, it is not limited to this list. Consider how the memory must be connected to choose which resistors should be populated.

- S26KS256SDDPBHV02

- S27KS0641DPBHI023

- APS6408L-OBM-BA

- MX25UM51345GXDI00

In this example, the MX25UM51345GXDI00 that is on port B is removed and placed on port A. Verify the memory signals that are needed by looking at the data sheet and comparing the signals to the EVK schematics. See below the necessary hardware changes.

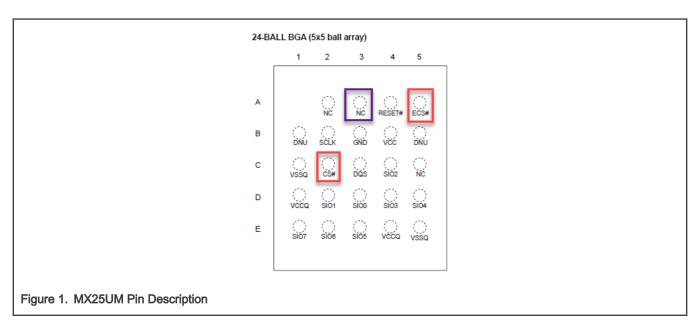

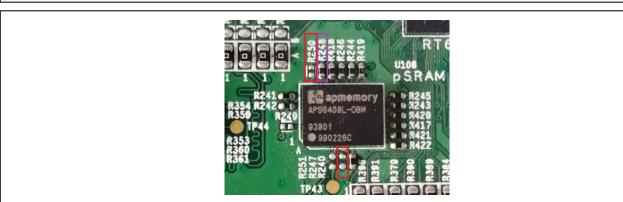

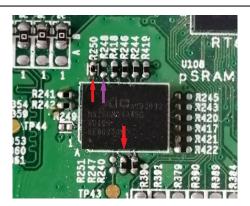

The evaluation board has several 0  $\Omega$  resistors that can be added or removed depending on the device that is used. In this case, the original setting shows that R250 (corresponds to A5) and R247 (corresponds to C2) are not populated. It means that there is no connection to these pins. However, for this memory these pins are necessary as they provide the chip select signal and the ECC correction signal, so they must be added (shown in red). In addition, A3 in this memory is not connected (NC), it corresponds to R248 that must be removed (shown in purple). See Figure 1.

Application Note 2/20

3 / 20

Figure 3. Original Setting of port A in RT685-EVK

Figure 4. New Setting of port A in RT685-EVK

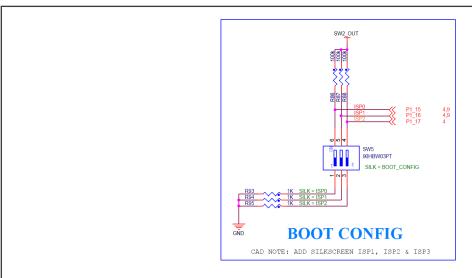

### 4.2 Changing ISP pins to select FlexSPI Port A

As mentioned previously, if the PRIMARY\_BOOT\_SRC bits in OTP are not set, the i.MX RT600 reads the status of the ISP pins to determine the boot source. Therefore, to boot from port A instead of port B, the ISP switches on the evaluation board must be changed to:

ISP0 -> High. SW5 pin 1 is off to create a pull-up.

ISP1 -> High. SW5 pin 2 is off to create a pull-up.

ISP2 -> Low. SW5 pin 3 is on to create a pull-down.

Figure 5. SW5 Schematic

Application Note 4 / 20

Figure 6. ISP pin configuration to boot from port A

#### 5 Flash loader modifications

For the debuggers to be able to load the SDK examples correctly, a flash loader is used. It contains various configurations for the external memory in use. In addition, the flash loader is configured to use Port B. To download and debug your application from the correct flash device on Port A, change the flash loader source code. The steps for flash loader modifications for MCUXpresso, IAR, and Keil are listed below.

### 5.1 Characteristics and register settings

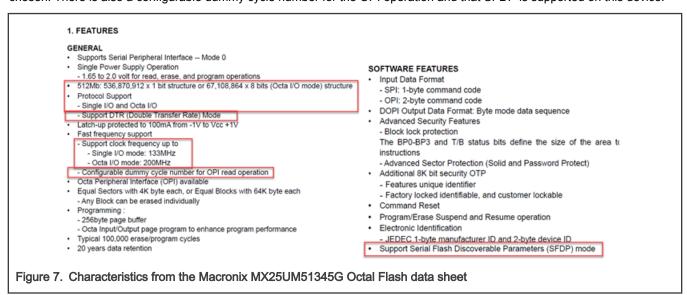

To understand how the characteristics of the device are translated into the register settings, look at the following characteristics from the Macronix MX25UM51345G Octal Flash data sheet.

Several characteristics are needed from the general and software features of the device. For example, the general features state that the device supports a single-bit structure as well as an 8-bit structure that can be applied to the number of bits in the data pad for flash access. Additionally, there is support for DTR and the maximum frequencies at which it can run depending on the mode chosen. There is also a configurable dummy cycle number for the OPI operation and that SFDP is supported on this device.

Although these are not all the characteristics to set the necessary register bits, you can understand how they can or cannot be configured. Examine the CONFIG\_OPTION0 register.

NOTE

See Appendix A, for the register options.

RT600 Flash Loader For Custom Flash Device, Rev. 0, 01 September 2021

| Option            | Description                                                                                                                                                                                                                                                              |                                                                                                                                 |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| device_type       | For the Macronix Octal Flash devices, there are tw                                                                                                                                                                                                                       | vo options:                                                                                                                     |  |  |  |  |  |  |

|                   | 4- Macronix Octal DDR                                                                                                                                                                                                                                                    | 4- Macronix Octal DDR                                                                                                           |  |  |  |  |  |  |

|                   | 5- Macronix Octal SDR                                                                                                                                                                                                                                                    | 5- Macronix Octal SDR                                                                                                           |  |  |  |  |  |  |

|                   | Both of these options are possible according to the appropriately for your application. In this example,                                                                                                                                                                 |                                                                                                                                 |  |  |  |  |  |  |

|                   | 24-BGA, 68-WLCSP                                                                                                                                                                                                                                                         | Octa I/O STR (MHz)                                                                                                              |  |  |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                          | Octa I/0 DTR (MHz)                                                                                                              |  |  |  |  |  |  |

| query_pad         | The query pad is the necessary number of pads to supported on this device, for more details of this cor of MX25UM.  The sequence of issuing RDSFDP instruction in SF (5Ah) → send 3 address bytes on SI pin→ send 8 du                                                   | mmunication see section 11-1 of the data sheet PI is CS# goes low → send RDSFDP instruction                                     |  |  |  |  |  |  |

|                   | RDSFDP operation can use CS# to high at any tin                                                                                                                                                                                                                          |                                                                                                                                 |  |  |  |  |  |  |

|                   | SFDP in SPI is a JEDEC standard, JESD216D.                                                                                                                                                                                                                               |                                                                                                                                 |  |  |  |  |  |  |

|                   | The sequence of issuing RDSFDP instruction in OPI/DOPI mode: CS# low→ send RDSFDP instruction (5Ah/A5h) → send 4 address bytes on SIO pin → send 20 dummy cycles → read SFDP code on SIO [7:0]→ to end RDSFDP operation can use CS# to high at any time during data out. |                                                                                                                                 |  |  |  |  |  |  |

|                   | According to the data sheet, it is possible to configure it for serial or octal communication. However, since SPI is a JEDEC standard, this paper uses the first setting for the 1-bit structure.                                                                        |                                                                                                                                 |  |  |  |  |  |  |

|                   | query_pad 19:16 Data pads during Query command (read SFDP or read MID)  0 - 1  2 - 4  3 - 8                                                                                                                                                                              |                                                                                                                                 |  |  |  |  |  |  |

|                   | Figure 8. Data pad options provided for query command                                                                                                                                                                                                                    |                                                                                                                                 |  |  |  |  |  |  |

| cmd_pad           | The CMD pad is the bit structure used for flash access. For this device, the 1-bit structure and the 8-bit structure are available. This example uses the octal setting.                                                                                                 |                                                                                                                                 |  |  |  |  |  |  |

|                   | cmd_pad 15:12 Data pads during Flash access command 0 - 1 2 - 4 3 - 8                                                                                                                                                                                                    |                                                                                                                                 |  |  |  |  |  |  |

|                   | Figure 9. Data pad options provided for flash access command                                                                                                                                                                                                             |                                                                                                                                 |  |  |  |  |  |  |

| quad_mode_setting | In Quad mode, flash transmits/receives data on 4 mode; therefore, the setting is 0.                                                                                                                                                                                      | In Quad mode, flash transmits/receives data on 4 Data pin. This device does not support quad mode; therefore, the setting is 0. |  |  |  |  |  |  |

| misc_mode         | Miscellaneous mode allows experimental settings, these settings are not recommended for a product and must be 0. If any setting applies to your device, review the data sheet.                                                                                           |                                                                                                                                 |  |  |  |  |  |  |

Table continues on the next page...

Application Note 6 / 20

#### Table continued from the previous page...

| max_freq | You can configure the frequency using the serialClkFreq file of the FlexSPI Flash Configuration block from the user manual. See Appendix A. In this example, option 1 indicates SDR mode 24 |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | MHz in normal boot mode.                                                                                                                                                                    |

The settings chosen are written in the CONFIG\_OPTION0 and CONFIG\_OPTION1 within the source code. The steps for each IDE are described below and the same setting is applied to all three.

CONFIG\_OPTION0 = 0xC0503001

CONFIG\_OPTION1 = 0x00000000

NOTE

See Appendix A, for OTP settings.

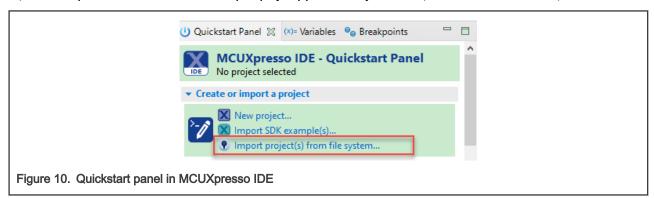

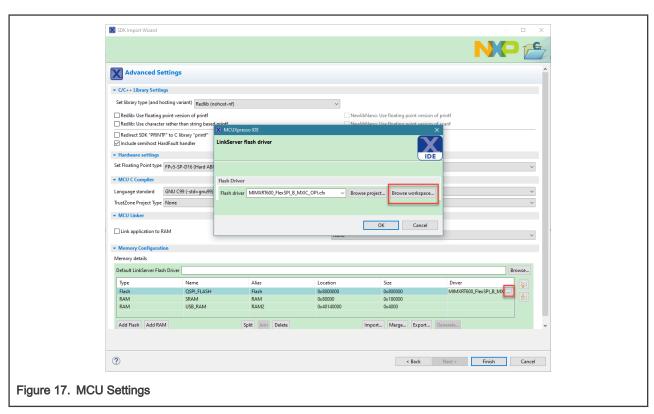

#### 5.2 Steps for the flash loader modifications for MCUXpresso

NOTE

Currently, the following steps are based on MCUXpresso + LPC-Link2. SEGGER's JLINK is not supported for the custom driver using MCUXpresso.

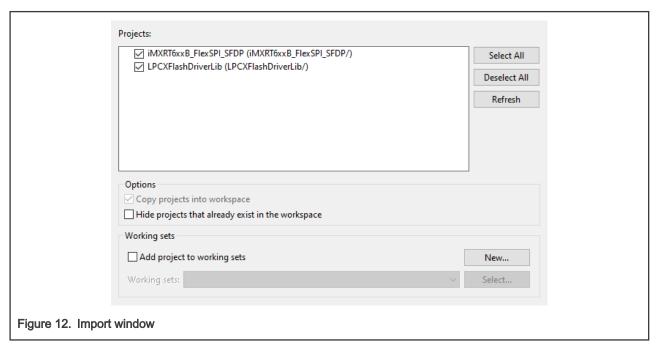

1. Open MCUXpresso IDE and select the "Import project(s) from file system..." option from the Quickstart panel.

2. In the Project archive (zip), browse for the following path where the flash loader drivers are located:

${\tt C:\nxp\MCUXpressoIDE\_11.x.x.xxx\ide\Examples\Flashdrivers\NXP\iMXRT}$

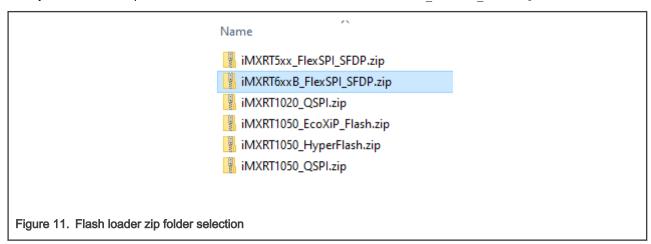

3. Here you find several zip folders for the i.MXRT families. Select the iMXRT6xxB FlexSPI SFDP.zip.

Application Note 7/20

4. Once the zip folder has been selected, click Next and select both projects: iMXRT6xxB FlexSPI SFDP and LPCXFlashDriverLib.

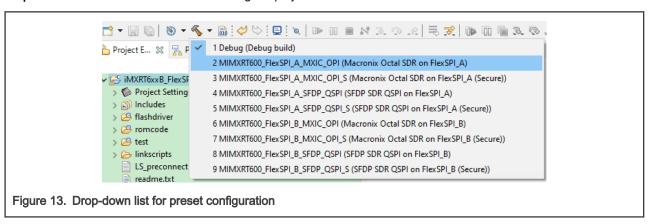

5. The imart6xxB flexspi sfdp project has some presets ready that can be chosen from. Find these options using the drop-down list in the Build icon when selecting the project.

There are settings ready and available for both ports A and B using the Macronix Octal flash device, as well as flash devices that support SFDP.

6. Open the FlashConfig.h file and scroll down to the enabled section for this option. It is presented as an if-else statement that enables or disables the configuration based on the chosen device. Replace the value for CONFIG OPTIONO and CONFIG OPTION1 with the setting chosen in section 5.1.

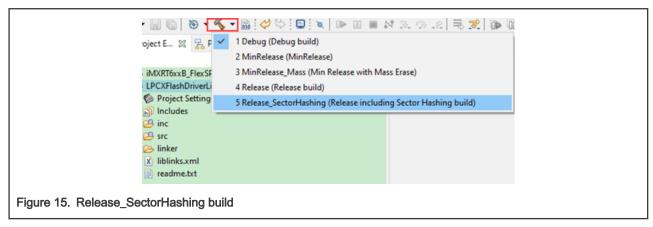

7. Before building the project, select "Release\_SectorHashing" for the LPCXFlashDriverLib project and build.

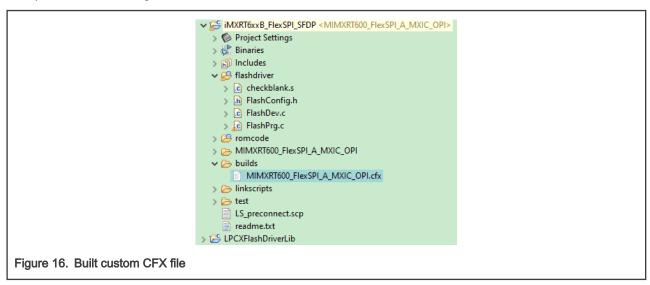

8. Build the imart6xxB\_FlexSPI\_SFDP project, the "builds" folder is created. It contains the CFX file necessary to boot from port A with the settings chosen for the Macronix Octal flash device.

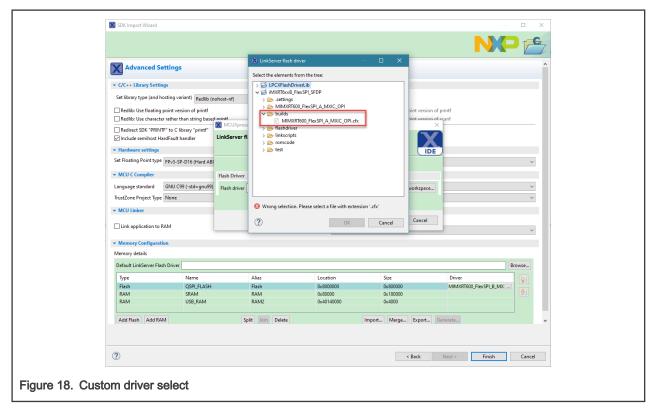

To test that this flash loader works, import the gpio\_led\_output example in the same workspace that flash loader drivers are in. In the Advanced Settings window of the SDK Import wizard, select the driver from the workspace option as seen below.

Application Note 9/20

10. Select the CFX file created from the builds folder.

11. Click Finish to close the SDK Import wizard. Next, open the flash\_config.c source file in the flash\_config folder of the gpio\_led\_output project. Change the sflashAlSize = 0 to the BOARD\_FLASH\_SIZE macro and replace the sflashBlSize with 0.

Application Note 10 / 20

```

(1u << kFlexSpiMiscOffset_SafeConfigFreqEnable) | (1u << kFlexSpi

58

.deviceType = 0x1,

.sflashPadType = kSerialFlash_8Pads,

59

50

.serialClkFreq = kFlexSpiSerialClk_DDR_48MHz,

51

.sflashA1Size = BOARD_FLASH_SIZE,

52

.sflashA2Size = 0,

53

.sflashB1Size = 0,

.sflashB2Size = 0,

.lookupTable =

Figure 19. Modify board flash size to match port A

```

12. Rebuild the project and run. You have successfully booted from port A.

#### 5.3 Steps for the flash loader modifications for IAR

1. For IAR, open the flash loader project from the following path in your PC:

```

C:\Program Files\IAR Systems\Embedded

Workbench 9.0\arm\src\flashloader\NXP\FlashIMXRT600 EVK FLEXSPI

```

- 2. To keep the changes locally, copy the flash loader project folder to your workspace.

- 3. In the FlashIMXRT600\_EVK\_FLEXSPI.c source file, replace the values for configOption.option0.U and configOption.option1.U with the setting discussed in section 5.1.

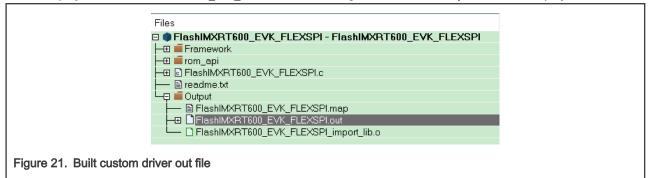

4. Build this project. The FlashIMXRT600 EVK FLAXSPI.out file is generated in the Output folder of the project.

Locate the IAR path:

C:\Program Files\IAR Systems\Embedded Workbench 9.0\arm\config\flashloader\NXP

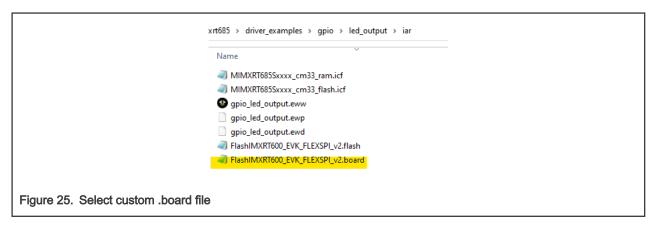

The .flash , .board , and .mac files are stored here for different NXP devices. Make a copy of the FlashIMXRT600\_EVK\_FLEXSPI.board and FlashIMXRT600\_EVK\_FLEXSPI.flash files. Add them to your application project folder, in this case the <code>gpio\_led\_output folder</code>.

Application Note 11/20

In this example, the copies are renamed:

- FlashIMXRT600 EVK FLEXSPI v2.flash

- FlashIMXRT600\_EVK\_FLEXSPI\_v2.board

- 6. Open the .flash file and replace the path where your local .out file is stored from step 4.

```

<

```

It is not necessary to modify the page or the block value. However, do so if your memory device has different values. They are recognized in the flashInit.

7. Open the .board file and replace the path that points to the new modified .flash file.

```

<

```

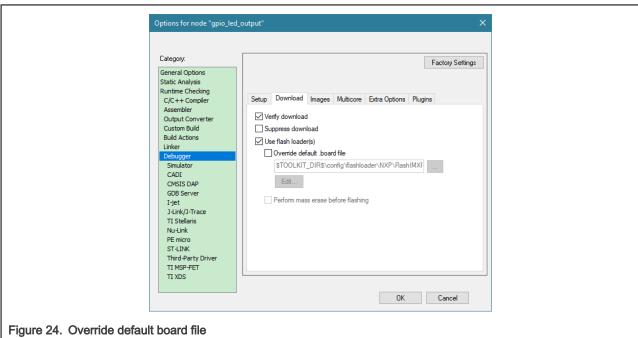

- 8. Save your changes and open the gpio led output example for the IAR IDE.

- Select the project and open the project options. Locate the Debugger > Download tab and select override default .board file.

10. Find the <code>gpio\_led\_output</code> project path and select the newly modified .board file and click **OK**.

RT600 Flash Loader For Custom Flash Device, Rev. 0, 01 September 2021

Application Note 12 / 20

11. Rebuild the project and run. You have successfully booted from port A.

### 5.4 Steps for the flash loader modifications for KEIL

- 1. For KEIL, open the flash loader project provided in the SW package.

- 2. In the FlashPrg.c source file, replace the values for CONFIG\_OPTIONO and CONFIG\_OPTION1 with the setting from section 5.1.

```

FlashPrg.c*

NXP LPC18xx/LPC43xx S25FL032 SPIFI Flash

25

26

28 ⊟/* History:

* Version 1.00

Initial release

31

33 #include <stdbool.h>

34 #include "../FlashOS.H"

// FlashOS Structures

35 #include <string.h>

36 #include "bl api.h"

#include "cmsis_compiler.h"

38

39 /** local definitions **/

#define FLASH_BASE_ADDR_0x0800000

#define CONFIG_OPTION0 0xc0503001

#define CONFIG_OPTION1 0x00000000

Figure 26. Config option new setting written

```

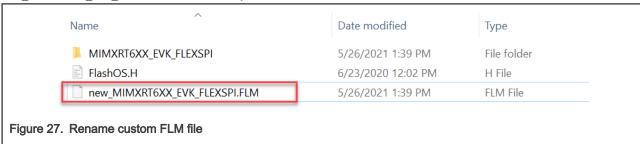

- 3. Build the project inside the workspace.

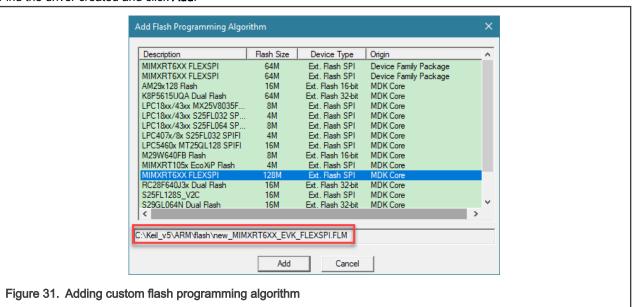

- 4. A MIMXRT6XX\_EVK\_FLEXSPI.FLM file is generated in the Output folder of the project. Change the name to new MIMXRT6XX EVK FLEXSPI.FLM to identify it later on.

5. Copy and paste this file in the following path:

C:\Keil v5\ARM\Flash

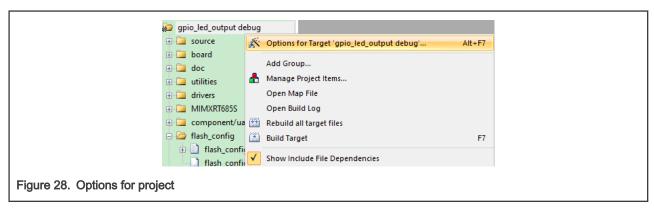

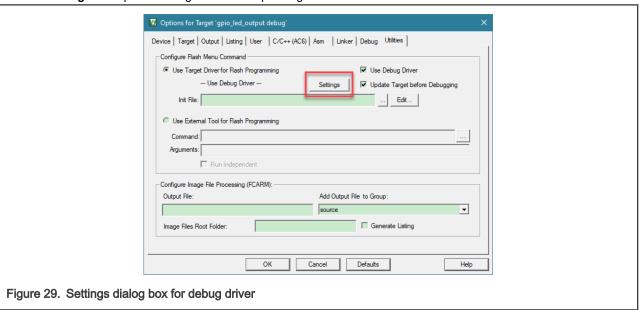

6. Select the project and open the **Options for Target**.... Locate the **Utilities** tab.

Application Note 13 / 20

14 / 20

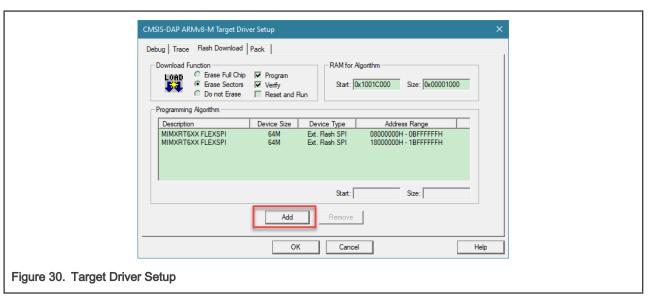

7. Click the settings and open the Target driver setup dialog box.

NOTE

See Appendix A , for .init file modifications.

- 8. The two loader paths that are shown are available from the predetermined settings. In this example, these two are removed and a new one with the modified flash loader is created.

- 9. Click the Add button to find the modified flash loader.

10. Find the driver created and click Add.

- 11. To save the project changes, click **OK**.

- 12. Rebuild the project and download. You have successfully booted from port A.

#### 6 Conclusion

This application note describes how to modify the flash loader source code step by step to boot from port A using the MIMXRT685-EVK. For more information, refer to "RT6xx User Manual".

#### 7 References

- RT6xx User manual (document: UM11147)

- MX25UM51345G Datasheet

Application Note 15/20

## 8 Revision history

Table 2. Revision history

| Revision number | Date              | Substantive changes |  |

|-----------------|-------------------|---------------------|--|

| 0               | 01 September 2021 | Initial release     |  |

## A Required options, settings, and modifications

The appendix gives required information on Option 0 and Option 1 definition, FlexSPI flash configuration block, FlexSPI boot configurations in OTP, settings of the shadow register, and LUT Section from .init file that may need to be modified.

1. Option0 definition in table 1004 of the RT6xx User manual.

Table 3. Table 1004. Option0 definition

| Field             | Bits  | Description                                            |

|-------------------|-------|--------------------------------------------------------|

| tag               | 31:28 | The tag of the config option, fixed to 0x0C            |

| option_size       | 27:24 | Size in bytes = (Option Size + 1) * 4                  |

|                   |       | It is 0 if only option0 is required.                   |

| device_type       | 23:20 | Device Detection Type                                  |

|                   |       | 0 - Read SFDP for SDR commands                         |

|                   |       | 1 - Read SFDP for DDR Read commands                    |

|                   |       | 2 - HyperFLASH 1V8                                     |

|                   |       | 3 - HyperFLASH 3V                                      |

|                   |       | 4 - Macronix Octal DDR                                 |

|                   |       | 5 - Macronix Octal SDR                                 |

|                   |       | 6 - Micron Octal DDR                                   |

|                   |       | 7 - Micron Octal SDR                                   |

|                   |       | 8 - Adesto EcoXiP DDR                                  |

|                   |       | 9 - Adesto EcoXiP SDR                                  |

| query_pad         | 19:16 | Data pads during Query command (read SFDP or read MID) |

|                   |       | 0- 1                                                   |

|                   |       | 2- 4                                                   |

|                   |       | 3– 8                                                   |

| cmd_pad           | 15:12 | Data pads during Flash access command                  |

| 0- 1<br>2- 4      |       | 0- 1                                                   |

|                   |       | 2- 4                                                   |

|                   |       | 3– 8                                                   |

| quad_mode_setting | 11:8  | Quad Mode Enable Setting                               |

Table continues on the next page...

Application Note 16 / 20

Table 3. Table 1004. Option0 definition (continued)

|           |     | 0 - Not configured                                                                                                                           |

|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

|           |     | 1 - Set bit 6 in Status Register 1                                                                                                           |

|           |     | 2 - Set bit 1 in Status Register 2                                                                                                           |

|           |     | 3 - Set bit 7 in Status Register 2                                                                                                           |

|           |     | 4 - Set bit 1 in Status Register 2 vis 0x31 command                                                                                          |

|           |     | This setting the flash to be configured into QPI mode. User code must reset the flash into SPI mode, the ROM does not do this automatically. |

|           |     | NOTE                                                                                                                                         |

|           |     | This field will be effective only if device is compliant with JESD216 only (9 longword SFDP table)                                           |

| misc_mode | 7:4 | Miscellaneous Mode                                                                                                                           |

|           |     | 0 - Not enabled                                                                                                                              |

|           |     | 1 - Enable 0-4-4 mode for High Random Read performance                                                                                       |

|           |     | 3 - Data Order Swapped mode (for MXIC OctaFlash only)                                                                                        |

|           |     | 5 - Select the FlexSPI data sample source as internal loop back, more details please refer                                                   |

|           |     | FlexSPI usage                                                                                                                                |

|           |     | 6 - Config the FlexSPI NOR flash running at stand SPI mode                                                                                   |

|           |     | NOTE                                                                                                                                         |

|           |     | Experimental feature, do not use in products, keep it as 0.                                                                                  |

| max_freq  | 3:0 | Max Flash Operation speed                                                                                                                    |

|           |     | 0 - Don't change FlexSPI clock setting                                                                                                       |

|           |     | Others – See fuse map of FlexSPI clock setting                                                                                               |

|           |     |                                                                                                                                              |

2. Option 1 definition in table 1005 of the RT6xx User manual.

Table 4. Table 1005.Option1 definition

| Field            | Bits  | Description                                                     |

|------------------|-------|-----------------------------------------------------------------|

| flash_connection | 31:28 | Flash connection option:                                        |

|                  |       | 0 - Single Flash connected to port A                            |

|                  |       | 1 - Parallel mode                                               |

|                  |       | 2 - Single Flash connected to Port B                            |

| drive_strength   | 27:24 | The Drive Strength of FlexSPI Pads                              |

| dqs_pinmux_group | 23:20 | The DQS pin mux Group Selection                                 |

| pinmux_group     | 19:16 | The pin mux group selection                                     |

| status_override  | 15:8  | Override status register value during device mode configuration |

Table continues on the next page...

Table 4. Table 1005.Option1 definition (continued)

| dummy_cycles | 7:0 | Dummy cycles for read command                      |

|--------------|-----|----------------------------------------------------|

|              |     | 0 - Use detected dummy cycle                       |

|              |     | Others - dummy cycles provided in flash data sheet |

3. Flash frequency in the FlexSPI flash configuration block. Table 997 in RT6xx User manual.

Table 5. Table 997. FlexSPI flash configuration block

| Field         | Offset | Size in | Description                                               |

|---------------|--------|---------|-----------------------------------------------------------|

|               |        | bytes   |                                                           |

| serialClkFreq | 0x046  | 1       | Flash Frequency. In Normal boot mode[BOOT_CFG[0]:bit7==0] |

|               |        |         | SDR mode:                                                 |

|               |        |         | 1 - 24 MHz                                                |

|               |        |         | 2 - 48 MHz                                                |

|               |        |         | DDR mode:                                                 |

|               |        |         | 1 - 48 MHz                                                |

|               |        |         | In High speed boot mode mode[BOOT_CFG[0]:bit7==1]         |

|               |        |         | SDR mode:                                                 |

|               |        |         | 1 - 30 MHz                                                |

|               |        |         | 2 - 50 MHz                                                |

|               |        |         | 3 - 60 MHz                                                |

|               |        |         | 4 - 80 MHz                                                |

|               |        |         | 5 - 100 MHz                                               |

|               |        |         | 6 - 120 MHz                                               |

|               |        |         | 7 - 133 MHz                                               |

|               |        |         | 8 - 166 MHz                                               |

|               |        |         | 9 - 200 MHz                                               |

|               |        |         | DDR mode:                                                 |

|               |        |         | 1 - 30 MHz                                                |

|               |        |         | 2 - 50 MHz                                                |

|               |        |         | 3 - 60 MHz                                                |

|               |        |         | 4 - 80 MHz                                                |

|               |        |         | 5 - 100 MHz                                               |

|               |        |         | 6 - 120 MHz                                               |

|               |        |         | 7 - 133 MHz                                               |

|               |        |         | 8 - 166 MHz                                               |

|               |        |         | 9 - 200 MHz                                               |

Application Note 18/20

4. The boot ROM is set to find devices that support 3B read by default. In some devices, the commands are different. Therefore, the OTP fuses must reflect the correct device.

Table 6. Table 998. FlexSPI boot configurations in OTP

| Field Name         | Enum Name       | Description                           | Offset | Width | Value |

|--------------------|-----------------|---------------------------------------|--------|-------|-------|

| FLEXSPI_FLASH_TYPE |                 | Define typical Serial NOR Flash types | 4      | 3     |       |

|                    | QSPI_ADDR_3B    | Device supports 3B read by default    |        |       | 000b  |

|                    |                 | Reserved                              |        |       | 001b  |

|                    | HYPER_1V8       | HyperFlash 1V8                        |        |       | 010b  |

|                    | HYPER_3V3       | HyperFlash 3V3                        |        |       | 011b  |

|                    | OSPI_DDR_MXIC   | MXIC Octal DDR                        |        |       | 100b  |

|                    | OSPI_DDR_MICRON | Micron Octal DDR                      |        |       | 101b  |

|                    |                 | Reserved                              |        |       | 110b  |

|                    |                 | Reserved                              |        |       | 111b  |

For development purposes, use the OTP shadow registers. It identifies the type of memory used while the device remains powered. If a power-on-reset occurs, this setting must be reconfigured.

For example, if you use a hyper flash in which the 3B read command is not supported, set the shadow register at the end of the main function as shown below.

5. If the specific memory requires, the .init file may be modified with respect to the LUT. Refer to the user manual to provide the correct settings of the LUT. In this application note example, it is not necessary since the LUT reflects the settings needed for the QSPI flash. Shown below is the section of the .init file that may need to be modified.

```

// Config look up table

__WDWORD(0x40134018, 0x5AF05AF0);

__WDWORD(0x4013401C, 0x2);

__WDWORD(0x40134200, 0x08200413);

__WDWORD(0x40134204, 0x00002404);

__WDWORD(0x40134208, 0x0);

__WDWORD(0x4013420c, 0x0);

Figure 33. LUT Section from .init file

```

RT600 Flash Loader For Custom Flash Device, Rev. 0, 01 September 2021

Application Note

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

**Limited warranty and liability** — Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

**Right to make changes** - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX,EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE, VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire+, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, elQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, μVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. M, M Mobileye and other Mobileye trademarks or logos appearing herein are trademarks of Mobileye Vision Technologies Ltd. in the United States, the EU and/or other jurisdictions.

© NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 01 September 2021

Document identifier: AN13386